Vivado HLS 勉強 その0

そろそろ高位合成にも手を出さなければということで、その準備 とりあえずチュートリアルで手を動かします。

参考資料

Vivado Design Suite ユーザー ガイド 高位合成 Vivado Design Suite Tutorial High-Level Synthesis UG871 (v 2014.1) May 6, 2014

ソースコードたち

Create New Project

ダウンロードしたフォルダのug871-design-files\Vivado_HLS_Tutorial\Introduction\lab1にソースコードが入っている。

Create New Projectでウィンドウが開く。

Project名と上記フォルダを指定します。

RTL化したいファイルを指定し、最上位関数の名前を指定します。

Testbenchのビヘイビアモデルを記述したファイルを指定します。

FPGAを指定します。ここではZedboardを指定しておきます。

次にクロック周期等を設定します。ひとまずクロック周期を5nsにします。

ソースコードを開く

Explorer > Source > fir.cでソースコードを開く

#include "fir.h" void fir ( data_t *y, coef_t c[N], data_t x ) { static data_t shift_reg[N]; acc_t acc; data_t data; int i; acc=0; Shift_Accum_Loop: for (i=N-1;i>=0;i--) { if (i==0) { shift_reg[0]=x; data = x; } else { shift_reg[i]=shift_reg[i-1]; data = shift_reg[i]; } acc+=data*c[i];; } *y=acc; }

Derective y, c, xの関数の最上位引数がモジュールのポートになります。

アレイ(x[] shift\reg)やループ(Shift_Accum_Loop)などは右クックすると最適化オプションを選択できます。

Run C Simulation

上のアイコンのRun C Simulationを押して開くダイアログをOKを押す。

******************************************* PASS: The output matches the golden output! ******************************************* @I [SIM-1] CSim done with 0 errors.

とConsoleに出ればOK

Run C Syntesis

Cソースコードの合成を行います。

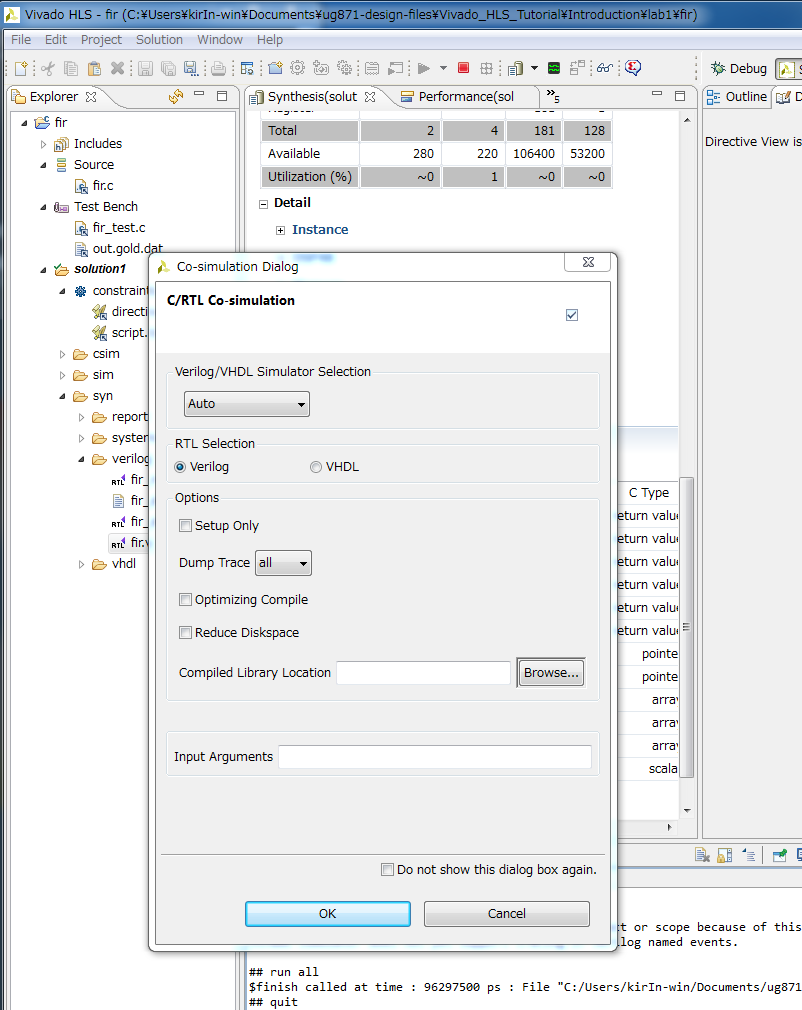

Run C/RTL Cosimulation

CやC++で書かれたテストベンチのデータをHDLシミュレータに入力してシミュレーションを行うようです。

Open Wave viewer